Theo Neowin, hai năm trước, IBM đã tiết lộ một quy trình sản xuất 7nm và Samsung có thể sẽ ra mắt chip 7nm vào năm 2018 tới. Tuy nhiên, thông báo mới được đưa ra bởi hai đối tác này đã đánh dấu một bước đột phá mới rất quan trọng trong việc thiết kế chip nói riêng và ngành công nghiệp bán dẫn nói chung.

Chip 5nm đạt được nhờ những bước đi mạo hiểm của các công ty trong việc phát triển công nghệ bán dẫn nano, mà cụ thể là công nghệ bóng bán dẫn gate-all-around (GAAFET). Cách tiếp cận ở đây được hiểu như là yêu cầu đòi hỏi các chất bán dẫn nano silic phải được tiếp xúc để tạo thành cấu trúc cơ bản của bóng bán dẫn. Điều này giúp tiết kiệm năng lượng và tối ưu hóa sức mạnh xử lý dựa vào hợp chất nano ở mức độ vi mô.

IBM tuyên bố rằng thiết kế GAAFET ấn tượng hơn so với FinFET sử dụng trong các chip hiện tại. Mặc dù FinFET có thể giảm xuống ở cấp độ 5nm nhưng đó là giới hạn trần trong thiết kế. Nói cách khác, kiến trúc GAAFET đơn giản hơn so với FinFET nhưng có thể được nhân rộng xuống cấp độ 3nm.

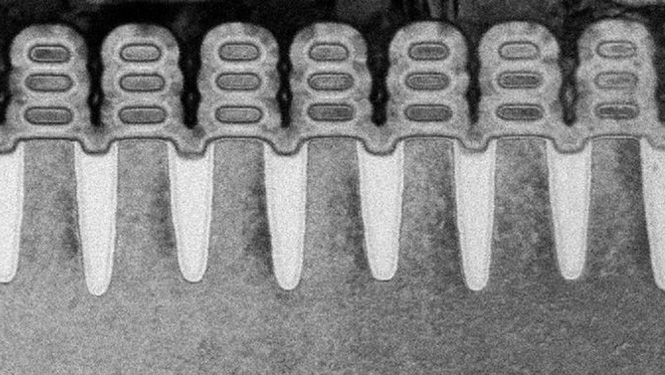

Một phần góc nhìn của công nghệ bóng bán dẫn GAAFET

|

Theo IBM, quy trình in bảng mạch bằng tia cực tím (EUV) được sử dụng ở đây cũng cho phép họ tiến hành điều chỉnh chiều rộng kích thước nm trong một thiết kế chip đơn, có nghĩa mạch in có thể được tinh chỉnh cho công suất và hiệu suất tốt hơn.

Bình luận (0)